### SELICON SEMICONDUCTOR Connecting the Silicon Semiconductor Community

Volume 41 Issue II 2020

🔰 @siliconsemi

**Plasma Dicing**

Technology

www.siliconsemiconductor.net

Ensure Wet Process Cleaning Success

### Structural Defects in a TO-220

Uncovering the Path to R&D Programmes

### Rely on SAM for 3D package analysis

By Panasonic

### **Inside** News Review, News Analysis, Features, Research Review, and much more... Free Weekly E News round up go to: www.siliconsemiconductor.net

Panasonic

Fully Automated AFM solution for OLED, 2D encoder, photomask and more

Gen 5

Gen 8+ Flat panel display glass

### Park NX-TSH

Gen 6

The automated Atomic Force Microscopy (AFM) system for ultra large and heavy flat panel displays at nanoscale

Gen 4

As the demand for Atomic Force Metrology for larger flat panel displays increases, Park NX-Tip Scan Head overcomes nanometrology challenges for samples over 300mm. The Tip Scanning Head and gantry style air-bearing stage allows Park NX-TSH to accurately image roughness measurement, step height measurement, critical dimension measurement. Learn more about how to get reliable, high resolution AFM images on your large sample size OLEDs, LCDs, photomasks using Park NX-TSH by watching our video at **parksystems.com/tsh/video**

Park

www.parksystems.com/nx-tsh inquiry@parksystems.com Visit us at Booth E7549 at Semicon China and at our Virtual Booth at Semicon West

## editor'sview

By Mark Andrews, Technical Editor

### Silicon technologies and 2020's new normal

IN THE RECENT PAST, the debut of new work-from-home products were welcome additions to a global portfolio of chip-enabled solutions. Yet these products hardly gained the notoriety that they do today. Six months ago, only epidemiologists used the word 'pandemic.' Now, more than a third of tech employees are working from home. This is 2020's New Normal.

While many of us are still trying to achieve balance between important and sometimes conflicting objectives, the pandemic has given us all a new perspective on what is important including the health we used to take for granted, family connections, and a collective future that is still being written.

No matter what is happening around us, technology continues to be a societal 'glue' that enables all types of work and life scenarios that were not imaginable mere months ago. I'm reminded of a former colleague from the Old School of business – He proudly called himself a Luddite – although a fantastic managers' role model, he couldn't quite get the knack of email. Today, he would flounder and fail. Even while tech industries face unprecedented challenges and opportunities, tech has emerged as the means by which we do business – We find community in team video conferencing; we find hope in social media posts by friends and family.

In this issue of Silicon Semiconductor, PVA TePla offers new insights into ways to test and inspect 3D packages through the use of scanning acoustic microscopy. JST provides insights into why effective wafer cleansing is critical to enabling

smaller device geometries. We look at more efficient, highly accurate wafer singulation technologies from Panasonic that reduce waste and increase throughput. We also explore ways that organizations often face gaps in their institutional knowledge when seasoned professionals retire or move on to new corporate homes. The article exploring 'Dark Data' from camLine discusses how an erosion of institutional knowledge can lead to repeats of failed experiments, while preserving this know-how can accelerate innovation.

'Business Unusual' has challenged us like never before. But we have also seen resilience across industries, demonstrating how we can productively live and work safely, even within our very changed world. Stay safe!

| Publisher & Editor Jackie Cannon           | jackie.cannon@angelbc.com      | +44 (0)1923 690205 |

|--------------------------------------------|--------------------------------|--------------------|

| Technical Editor Mark Andrews              | mark.andrews@angelbc.com       |                    |

| Sales & Marketing Manager Shehzad Munshi   | shehzad.munshi@angelbc.com     | +44 (0)1923 690215 |

| USA Representatives Tom Brun Brun Media    | tbrun@brunmedia.com            | +001 724 539-2404  |

| Janice Jenkins                             | jjenkins@brunmedia.com         | +001 724-929-3550  |

| Director of Logistics Sharon Cowley        | sharon.cowley@angelbc.com      | +44 (0)1923 690200 |

| Design & Production Manager Mitch Gaynor   | mitch.gaynor@angelbc.com       | +44 (0)1923 690214 |

| Circulation Director Scott Adams           | scott.adams@angelbc.com        | +44 (0)2476 718970 |

| Chief Executive Officer Stephen Whitehurst | stephen.whitehurst@angelbc.com | +44 (0)2476 718970 |

Joint Managing Director

Sukhi Bhadal

sukhi.bhadal@angelbc.com

Joint Managing Director

Scott Adams

scott.adams@angelbc.com

Is

Directors

Jackie Cannon. Sharon Cowley

bc.com +44 (0)2476 718970 bc.com +44 (0)2476 718970

Published by Angel Business Communications Ltd, Unit 6, Bow Court, Fletchworth Gate, Burnsall Road, Coventry CV5 6SP, UK. T: +44 (0)2476 718 970 F: +44 (0)2476 718 971 E: info@angelbc.com

Silicon Semiconductor is published four times a year on a controlled circulation basis. Non-qualifying individuals can subscribe at: £50.00/€60 pa (UK & Europe), £70.00 pa (Outside Europe), \$90.00 pa (USA). Cover price £4.50. All information herein is believed to be correct at time of going to press. The publisher does not accept responsibility for any errors and omissions. The views expressed in this publication are not necessarily those of the publisher. Every effort has been made to obtain copyright permission for the material contained in this publication. Angel Business Communications Ltd will be happy to acknowledge any copyright oversights in a subscequent issue of the publication. Angel Business Communications Ltd 2020. All rights reserved. Contents may not be reproduced in whole or part without the written consent of the publishers. The paper used within this magazine is produced by chain of custody certified manufacturers, guaranteeing sustainable sourcing. US mailing information Semiconductor is published four times a year for a subscription of \$90.00 by Angel Business Communications Ltd. Will 6, Bow Court, Fletchworth Gate, Burnsall Rd, Coverthy CV5 6SP UK. Periodicals postage paid at Rahway, NJ. POSTMASTER: send address changes to: Silicon Semiconductor, c/o Mercury International Ltd, 365 Blair Road, Avenel, NJ 07001. Printed by: The Manson Group. © Copyright 2020. ISSN 2050-7798 (Print) ISSN 2050-77801 (Online).

We strive for accuracy in all we publish; readers and contributors are encouraged to contact us if their recognise an error or omission. Once a magazine edition is published [online, in print or both], we do not update previously published articles to align old company names, branding, marketing efforts, taglines, mission statements or other promotional verbiage, images, or logos to newly created or updated names, images, typographic renderings, logos (or similar) when such references/images were accurately stated, rendered or displayed at the time of the original publication. When companies change their names or the images/text used to represent the company, we invite organizations to provide Angel Business Communications with a news release detailing their new business objectives and/or other changes that could impact how customers/prospects might recognise the company, contact the organization, or engage with them for future commercial enterprise.

## CONTENTS

### 12 COVER STORY

Panasonic's plasma dicing for higner throughput and increased yield per wafer

Plasma dicing addresses the challenges of dicing smaller and thinner dies

### 18 Structural defects in TO-22 32 Enabling smaller,

Ultrasound and X-ray work together to image and evaluate harmless anomalies and potential field failures in a TO-220 package.

### 22 Wet process cleaning equipment success

Expert consultation can keep semiconductor production on track through installation and beyond.

### 26 Carrier profiling in high vacuum using SSRM and SCM

Scanning Spreading Resistance Microscopy (SSRM) and Scanning Capacitance Microscopy (SCM) are both established scanning probe-based methods for two-dimensional carrier profiling.

### 32 Enabling smaller, lowerpower IoT & wearables

SiTimes makes a case for MEMS oscillators versus quartz-crystal-based clocking sources.

### 40 Dark Data: Uncovering the path to accelerating R&D programmes

At a time when Baby Boomers are retiring in record numbers, companies are discovering that when seasoned employees leave, they frequently take information with them that could speed future R&D programmes while avoiding unnecessary experimentation.

### 44 Rely on SAM for 3D package device analysis

The emergence of highly accurate wafer bonding and die stacking has enabled new generations of 3D semiconductors.

Log(Ohm)

Resistance [Log(Ohm)]

Vacuum Ambient

### news

Increa force

06 SUSS MicroTec and Micro Resist Technology partner in advancing nanoimprint lithography

X [um

- 07 Onto Innovation announces three new metrology systems

- 08 Imec overcomes fundamental operation challenge for voltage controlled RAM

- 09 OLED rising market marks new era in lighting and screen technology

- 10 ACM Research launches 18-chamber single-wafer cleaning tool

## SUSS MicroTec and Micro Resist Technology partner in advancing nanoimprint lithography

SUSS MicroTec, supplier of equipment and process solutions for the semiconductor industry, and micro resist technology GmbH, a leading company for the development and production of innovative photoresists and advanced nanoimprint materials, announced today their cooperation on Nanoimprint Lithography (NIL).

NIL is a key enabler of the additive manufacturing revolution through highfidelity pattern transfer. This UV-curing stamping process is increasingly used in the production of future emerging application in photonics, such as diffractive optical elements in augmented reality glasses or for face recognition as well as for the transfer of micro- and nanoscale structures, e.g. in optical sensors, laser nano-PSS (Patterned Sapphire Substrates) or for anticounterfeiting.

The requirements for nanoimprint lithography and its applications are continuously changing. Therefore, the fundamental objective of the cooperation is to understand newly emerging requirements and to solve them by implementing solutions at both process and materials level, thus addressing the high challenges set by the players in this industry. High quality imprint is based on three pillars: equipment, process and materials. The first two pillars, equipment and high-volume process manufacturing expertise, are addressed within the SUSS Imprint Excellence Center, a combined venture of SUSS MicroTec Lithography GmbH and SUSS MicroOptics SA. This constellation is further complemented and strengthened by joining the third pillar: the chemical expertise of the nanoimprint material supplier micro resist technology GmbH. The combination of these three pillars allows to better serve the high demanding need of the industry with its ever more challenging requirements on the replication of nanostructures.

"The SUSS Imprint Excellence Center leverages on decades of experience in imprinting equipment together with broad industrial process development in highvolume manufacturing environment," said Franz Richter, CEO of SUSS MicroTec, "Further strengthening this cluster through a strong partnership with a leading resist supplier and experienced material manufacturer is mandatory in order to enable the perfect imprinting solutions." Involved companies are dedicated to pursue the deepening of their cooperation, with the common goal, to push further the development of existing and new applications towards both high performance and high volume production.

"For more than two decades, micro resist technology has provided tailor-made resist formulations for NIL around the globe", said Ms. Gabi Grützner, CEO and founder of MRT. "Our profound know-how on polymer chemistry and replication processes allows us to provide stateof-the-art material solutions which addresses a growing number of industrial use-cases where replication technology is applied for the manufacturing consumer products.

"We are delighted about the cooperation with our partner within the alliance since our customers success of industrial imprint processes can be streamlined when materials and equipment are attuned to each other. This is the great opportunity we see in the SUSS Imprint Excellence Center as the right package is delivered to the community to make NIL available to more industrial users."

### Picosun's medical ALD solutions

Picosun Group reports excellent results in ALD-organic bilayer encapsulation of metal electrodes for neuroprosthetics and bioelectronic medicine. Group also reports superior hermetic barrier performance of its ALD nanolaminates against corrosive ion diffusion in aqueous media. This is an important result for medical ALD applications and implantology, where metal components and sensitive microelectronics need to be protected against corrosion caused by human body fluids.

Picosun's ALD nanolaminates were proven to completely block the diffusion of Na+, K+, Cl- and PO43- ions, which are known to be amongst the most corrosive ionic species in aqueous media [1]. Tests were performed at 87 °C PBS (phosphate-buffered saline) solution for 2 months (see Figure 1). Several of Picosun's ALD materials have been proven non-cytotoxic and safe for human tissues already earlier [2], which gives great flexibility for designing tailored nanolaminate encapsulants for varying substrates and levels of protection.

For (platinum) metal electrode protection, ALD HfO2 was first used as an attachment and innermost barrier layer deposited right against the metal, and biocompatible organic polymer PDMS (polydimethylsiloxane) was applied on top of the ALD film to create impermeable, stable bilayer protection combing the best properties of both materials [3]. ALD HfO2 provides good adhesion to and hermetic sealing of the surface, whereas PDMS, as the more "macroscopic" layer, robustness and sturdiness on top of the ultra-thin ALD film. The bilayer coatings were tested by soaking them in PBS solution for 450 days at room temperature.

The results of both tests again support ALD's enormous potential to provide totally new solutions to the challenges medical device industries are facing. The constant trend of increased miniaturization and system-level integration of microelectronics drives the same development in implantable medical devices as well. When the device size decreases but its complexity and the time the device spends inside human body increase, traditional encapsulation methods fail.

## Onto Innovation announces three new metrology systems

ONTO INNOVATION INC. announced the availability of a suite of process control metrology solutions for advanced device manufacturing. The suite of optical metrology solutions was developed for next generation semiconductor devices to enable high precision, high accuracy, and high productivity solutions for Gen6, 3D NAND, leading 5nm/3nm logic and advanced 1alpha DRAM devices.

This new metrology suite represents the first exciting results from Onto Innovation's enhanced R&D team to create a comprehensive solution set that capitalizes on its extensive leadership in optical metrology and enhancements in a new machine learning engine software for all of these applications.

Kevin Heidrich, senior vice president of marketing, commented, "We are very excited by our customers' early responses to the performance and value of these new systems. Our measurement data analysis from advanced logic and memory devices has been found to be highly correlated to our customers' metrology lab standards such as CD-SEM and TEM, which means they can continue to use high-speed optical metrology systems without the need to use significantly slower, and more costly, X-ray technology."

He continued, "For the most advanced 3D NAND devices, the challenges to measure the very high aspect ratio channel holes and word lines, with aspect ratios much greater than 80:1, are forcing customers to consider slower X-ray tools and other destructive measurement techniques. Similarly, for the most advanced DRAM and logic devices, complex transistor structures and new materials at the 5nm and 3nm nodes have customers looking at new methods of metrology for the critical gate-all-around/nano-sheet processing steps. Onto Innovation has developed platforms that drive optical technology to the next level enabling the advantages of both high sensitivity and high productivity, providing customers information at the rate and quality that

is needed for process development and high-volume manufacturing."

The new Atlas V metrology system is designed to measure several key steps that include buried features, not visible by CD-SEM and other techniques. The sensitivity of Atlas V metrology enables these critical dimensions to be measured with high accuracy and sensitivity, extending the capability of optical solutions for generations of devices and eliminating the need for other slower process control techniques.

Atlas V technology now enables the performance needed for customers' development of gate-all-around devices and is over 100 times faster than X-ray solutions for these structures. Onto Innovation's customers that have validated this new OCD technology and have already seen the speed and resolution that was once thought to be beyond the limits of optical technology.

The IMPULSE V system, built on a history of industry leading reliability, enables higher productivity and higher performance for next generation integrated metrology. The system is designed to work seamlessly with chemical mechanical polishing (CMP) systems to provide high throughput run-to-run control for critical process steps. The IMPULSE V system enables recipe inter-operability with the Atlas V system for uninterrupted production recipe setup and optimization. Utilizing the latest machine learning technology, the IMPULSE V technology supports on-device metrology enabling broad flexibility and high process coverage

enabling higher productivity with broader process recipe coverage.

The new Aspect metrology system is a revolutionary optical platform that is designed for the current and future challenges of advanced 3D NAND devices. Memory density increases with both layer-pair scaling and tier stacking for memory stacks well over 200 pairs. The Aspect technology was designed with these future architectures and scaling strategies in mind. Aspect metrology is demonstrating performance superior to X-ray systems across multiple customer devices through a revolutionary infrared optical system providing full profiling capability to enable critical etch and deposition control, with the speed and process coverage that customers require.

Al-Diffract Technology is the key component of the new solution suite. It is the software analysis engine powering all of these leading metrology systems. This new product now provides up to 90% faster time to solution using the Al-Diffract engine which extends the industry leading NanoDiffract® software by leveraging extensive machine learning capabilities along with high fidelity modeling. The result is a simultaneous improvement in metrology performance along with a significant time to solution reduction.

All products are shipping to select customers this quarter, with broad availability by the fourth quarter. The company expects revenue to begin in the fourth quarter and ramp in the first half of 2021.

## Imec overcomes fundamental operation challenge for voltage controlled RAM

AT the 2020 Symposia on VLSI Technology and Circuits, imec, a leading research and innovation hub in nanoelectronics and digital technologies, presents a deterministic write scheme for voltage-controlled magnetic anisotropy (VCMA) magnetic random access memories (MRAMs), obviating the need for pre-reading the device before writing. This significantly improves the write duty cycle of the memory, enabling ns-scale write speeds.

As a second improvement, a manufacturable solution for externalfield-free VCMA switching operation was demonstrated. Both innovations address fundamental write operation challenges for VCMA MRAMs, making them viable candidates for future high-performance low-power memory applications.

Voltage-controlled MRAM operation has recently been introduced to bring down the power consumption of spin-transfertorque MRAM (STT-MRAM) devices – which is a class of non-volatile, highdensity, high-speed memories.

While writing STT-MRAM memory cells is performed by means of a current (injected perpendicular into a magnetic tunnel junction), VCMA MRAM uses an electric field (hence, a voltage) for its write operation – which is far less energy consuming. Two basic components are required to switch from the parallel (P) to the antiparallel state (AP) (or vice versa): an electric field (across the tunnel barrier) to remove the energy barrier, and an external in-plane magnetic field for the actual VCMA switching.

Imec has now solved two fundamental operation challenges which have so far limited the write speed and manufacturability of VCMA MRAMs, respectively. The slow write operation relates to the unipolar nature of the VCMA MRAM device: the same polarity of write pulse is needed to transition from the parallel to the anti-parallel (P-AP) state as to switch from anti-parallel to parallel (AP-P) state.

Therefore, the memory cell needs to be 'pre-read' to know its state before writing – a sequence which significantly slows down the write operation. Imec has introduced a unique deterministic VCMA write concept that avoids the need for pre-reading: distinct threshold voltages are introduced for the A-AP and AP-P transitions by creating an offset in the energy barrier. This offset is realized by implementing a small (e.g. 5mT) offset magnetic field (Bz,eff) in the VCMA stack design.

As a second improvement, imec embedded a magnetic hardmask on top of the magnetic tunnel junction. This eliminates the need for an external magnetic field during VCMA switching, improving the device's manufacturability without degrading its performance.

The devices were fabricated using imec's 300mm state-of-the-art technology infrastructure, proving their compatibility with CMOS technology. Reliable 1.1GHz (or ns-scale speed) externalmagnetic-field-free VCMA switching was demonstrated with only 20fJ write energy. A high tunnel magnetoresistance of 246% and an endurance of more than 1010 have been achieved. Gouri Sankar Kar, Program Director at imec: "These characteristics bring VCMA MRAM performance beyond STT-MRAM operation, making the devices ideal candidates for high-performance, low-power and high-density memory application - serving advanced computational needs or analog computein-memory applications."

### GLOBALFOUNDRIES acquire land in NY for new manufacturing facility

GLOBALFOUNDRIES, the specialty foundry and the leading U.S. pure-play manufacturer of semiconductors, has announced it has secured a purchase option agreement for approximately 66 acres of undeveloped land adjacent to its most advanced manufacturing facility, Fab 8, in Malta, N.Y., near the Luther Forest Technology Campus (LFTC).

The land parcel is located at the southeast end of the New York State Energy Research and Development Authority (NYSERDA) Saratoga Technology + Energy Park (STEP) campus, adjacent to Stonebreak Road Extension, between GF's Fab 8 facility and Hermes Road. Exercising the option to purchase the land and commencement of development to expand GF's Fab 8 facility will be subject to zoning regulations and client demand. The parcel is being sold at Fair Market Value, with a purchase price determined by an independent appraiser. "Amid growing consensus in our nation's capital for investment in semiconductor manufacturing, it's more important than ever that we are ready to fast track our growth plans at GLOBALFOUNDRIES' most advanced manufacturing facility in the U.S.," said Ron Sampson, senior vice president and general manager of U.S. Fab Operations at GF. "With this agreement option, we now have additional flexibility to expand our footprint and position Fab 8 for future growth in Saratoga County and New York State, while strengthening U.S. leadership in semiconductor manufacturing."

"GLOBALFOUNDRIES continues to demonstrate its commitment to economic growth in Saratoga County and Upstate New York," said Darren O'Connor, Malta's Town Supervisor. "I am pleased to hear that this latest step will enable future growth opportunities for GLOBALFOUNDRIES for years to come." GF employs nearly 3,000 people and has invested over \$13 billion in Fab 8, its most advanced manufacturing facility in upstate New York. The company recently announced it is bringing its most advanced Fab 8 facility in upstate New York into compliance with both the U.S. International Traffic in Arms Regulations (ITAR) standards and the highly restrictive Export Control Classification Numbers (ECCNs) under the Export Administration Regulations (EAR).

## OLED rising market marks new era in lighting and screen technology

The OLED panel market is forecasted to grow at a CAGR of 12.9% during 2020-2025 to reach 45.55 billion units by 2025. While there will be a slight downturn overall due to Covid-19 pandemic, industry experts continue to expect OLED panels to be a significant display technology trend adopted across the world, with larger screen sizes, improved 8K resolution and new form factors.

Atomic Force Microscope manufacturer, Park Systems has scaled up its AFM tools for Gen8+ and all large flatpanel displays with the Park NX-TSH (Tip Scanning Head) system. It is the industry's only automated Tip Scan Head for analyzing samples larger than 300 mm. "Park NX-TSH is designed for large and heavy flat-panel display glass and 2D encoders, with integrated micro probe stations for conductive AFM and electric defect analysis." explains Keibock Lee. Park Systems President, "Park NX-TSH can scan up to 100  $\mu$ m x 100  $\mu$ m (x-y direction) and 15  $\mu$ m (z direction), and it has a flexible chuck to accommodate samples larger than 300 mm and heavier than 1 Kg-engineered for OLED, LCD and other large sample analysis."

Organic Light Emitting Diode (OLED) technology is being used in an increasing number of application areas because they can be flat, paper-thin and flexible, and have the ability to diffuse light, which is expected to significantly drive the market growth over the next few years. Park Systems, in anticipation of the market expansion, has developed Park NX-TSH specifically for manufacturers setting up fabs that produce nextgeneration flat-panel displays with the objective of overcoming the 300 mm sample size limit. Using conductive AFM, Park NX-TSH can measure the sample's electrical properties by supplying current through the optional probe stations.

The enabling technology for Park NX-TSH is the tip scanning head attached to the gantry that moves to the desired measurement positions on the surface of the sample that is fixed on a sample chuck. The Park NX-TSH tip scanning head system therefore overcomes the limitations of sample size and weight.

OLEDs, the next advance in lighting, differ from LEDs in that the semiconductors used to convert electricity into light are not synthetic single crystals but rather films composed of organic molecules.

The organic component makes them lighter and more energy efficient. Large panels can be assembled and stretched into unique displays, enhancing architectural design. Furthermore, it is even more sustainable given that OLEDs do not contain mercury, so when in widespread use they can save enormous amounts of hazardous waste.

### Park Systems Announces NanoScientific Symposium

PARK SYSTEMS will be presenting 'NanoScientific Symposium on Nano Applications for a Changing World' sponsored by Physics World and Nanotechnology World Association. It will be held online Oct. 14-15, 2020.

Park Systems launched this online event for researchers and scientists in nanoscience and nanotechnology to share data on how new nano applications under research will lead to discoveries that have positive impact on the world. The idea is that attendees will join together in a worldwide effort to understand to create breakthroughs in scientific discovery of how nanoparticles interact with matter and human physiology and how this knowledge can be harnessed to create a smarter future.

Nanometrology plays an important role in helping researchers understand how nanoparticles interact with matter, gas and the environment, showing in nano detail how individual cells react to various stimulus. Labs worldwide benefit from the advent of nanoscopic tools that give them clear images in real time.

"NanoTechnology World Association and Park Systems are showcasing the worldwide collaboration of our scientific communities to enrich our vulnerable planet and humanity with unprecedented scientific advances that inspire leadership roles in sustainability," says Marine Le Bouar, CEO, Nanotechnology World Association.

The Symposium is accepting presentation abstracts. In an effort to expedite the abstract submission process, please send a short abstract (can be 300 words or less) about your work in nano materials by July 30, 2020. Submit your abstract to: debbiewest@nanoscientific.org

## ACM Research launches 18-chamber single-wafer cleaning tool

ACM Research, Inc, a supplier of wafer cleaning technologies for advanced semiconductor devices, has announced from SEMICON China its Ultra C VI single wafer tool, the newest addition to its line of Ultra C cleaning systems. The Ultra C VI targets high-throughput cleaning of dynamic random-access memory (DRAM) and 3D NAND Flash devices to support increased production scale. Building on ACM's proven multi-chamber technology, the new tool features 18 chambers, representing a 50-percent expansion on the throughput and 12 chambers included in the Ultra C V system, with the same tool width and only slightly larger in length to allow for integration into existing production lines.

"Although memory devices are increasing in complexity, they still have the same high throughput requirements," said ACM's president and CEO Dr. David Wang. "Additional cleaning chambers enable memory device makers to support extra processing steps and more sophisticated drying technology, while maintaining or reducing production cycle time. We see an 18-chamber configuration as the sweet spot for this application. Compared to systems with higher chamber counts, the Ultra C VI provides a better balance for waferper-hour requirements and factoryautomation matching."

The Ultra C VI performs singlewafer cleaning for advanced DRAM devices of 1y nm and beyond, as well as advanced 3D NAND devices with 128 stacked layers and above. It can be used for a variety of front-end-of-line (FEOL) and back-end-of-line (BEOL) processes, depending on the application and the chemistries involved, such as BEOL polymer removal, tungsten- or copperloop post-cleans, pre-deposition cleans, post-etch and post-chemical mechanical planarization (CMP) cleaning, deeptrench/via cleans, and RCA standard cleans.

Multiple chemical combinations can be used during cleaning, including standard clean (SC1, SC2), hydrofluoric acid (HF), ozonated deionized water (DI-O3), diluted sulfuric peroxide mixture (DSP, DSP+), solvent cleaner, or other process chemicals. Up to two chemicals can be reclaimed and reused, which helps reduce the cost of consumables and overall cost of ownership. The Ultra C

VI can accommodate optional physical assistant cleaning methods, such as dual-fluid N2 spray cleaning or ACM's proprietary SAPS and TEBO megasonic cleaning technologies. It also offers an isopropyl alcohol (IPA) drying function that can be applied to patterned wafers with high aspect ratios. Moreover, as it fits within the same width as ACM's existing tools, this tool helps improve fab utilization and further contributes to lower cost of ownership. ACM plans to deliver the Ultra C VI tool to a leading memory manufacturer for evaluation and qualification in the third quarter of 2020.

### Pfeiffer Vacuum introduces next generation gas analyzers

OmniStar and ThermoStar GSD 350 are compact, portable benchtop analyzers for analyzing gases at atmospheric pressure. They are particularly used for applications in chemical processes, in the semiconductor industry, metallurgy, fermentation, catalysis, freeze-drying and environmental analysis. The gas inlet is fitted with a heated capillary for use at up to 350°C. This prevents vapors from condensing during process gas analysis. Thanks to the two-stage inlet system, an almost segregation-free gas supply is possible.

The ThermoStar solution was specially developed for coupling with thermo balances. The inlet system with a quartz capillary and a platinum orifice ensures that even the smallest concentrations can be analyzed. The OmniStar was developed for a wide range of applications and uses a stainless steel capillary as well as a valve which can interrupt the sample gas stream. Unlike other analytical methods such as FTIR or GC-FID, the two new devices allow simultaneous detection of all gases within the mass range.

With the new PV MassSpec software, it is possible to perform qualitative and quantitative analyses. This software offers a clear and user-friendly platform for recording and displaying measurement data and parameter settings. Even complete measuring procedures can be programmed and automated. With a variety of equipment variants available, the mass ranges of 1 to 100 u, 1 to 200 u and 1 to 300 u are covered. The two new models differ from comparable devices by their compact size and easy operation using an integrated 7 touch display or a web user interface. The device can be fully controlled and the user can also perform simple measurements without a PC or PV MassSpec via a smartphone or tablet.

The low detection limit (depending on the mass range) of up to <100 ppb, the low gas consumption of 1 - 2 sccm and the fast measuring time (up to 1 ms/u) characterize the new analytical instruments. For extended process customization, an integrated mass calibration device or a controlled purge gas system for corrosive gases are available.

### **Registration is Now Open**

### SEMICON<sup>®</sup> 50 VEST<sup>®</sup> 50 YEARS

### JULY 20-23, 2020 VIRTUAL EVENT

### Yes, you heard it right, SEMICON West 2020 is going virtual!

semi

Join us online for LIVE and On-Demand programs from the comfort of your home or work office using any mode of connection through your laptop, desktop, tablet, or mobile device. You'll have four days of programs on electronics manufacturing and design topics presented by experts and driven by technology and innovation.

### **EXPERIENCE LIVE KEYNOTES**

- Al Gore, Former United States Vice President

- Gary Dickerson, Applied Materials

- John E. Kelly III, IBM

- Tetsuro Higashi, Tokyo Electron

- Steve Brown, The Innovation Ultimatum

- Lea Gabrielle, Global Engagement Center U.S. State Department

- Plus many more

Accessible On-Demand 24/7 through Sept. 20

### PROGRAMS

- Bulls & Bears

- SEMI Market Symposium

- Test Vision Symposium

- imec

- SOI Industry Consortium

- Southeast Asia Pavilion

- Diversity & Inclusion

- TechTALKS

Lam

• SMART Pavilions

EDWARDS

GOLD SPONSORS

Get your All-In Pass for access to all the LIVE and On-Demand program content and more!

### **#SEMICONWest**

in 🕑 @SEMIAmericas

www.SEMICONWest.org

SCIENTIE

### Panasonic Plasma Dicing

For higher throughput and increased yield per wafer

Plasma dicing addresses the challenges of dicing smaller and thinner dies.

#### **BY PANASONIC**

EVERY PERSON with a passing interest in electronics has heard of Moore's Law: the processing power of affordable CPUs – or the number of transistors on a chip - will roughly double every two years. It is credit to both Gordon Moore's foresight, and the technical and engineering teams around the world who continue to innovate, that the 'Law' is still even being discussed today.

Part of the reason for chip size reduction lies in the shrinking of technology nodes (process geometries). Currently the smallest node that is being manufactured in mass volume is 7nm, and even smaller sizes are under development in the industry. The increase in processing power and speed and the miniaturisation and integration of electronic functions that continue to result from such technological advances lie at the heart of the pervasiveness of electronics in our everyday lives: the smart phones that we rely on; the uptake of artificial intelligence in smart homes and cities; driverless vehicles; remote medical home diagnostics – there is not one aspect of life that electronic products and systems have not penetrated.

But for this to continue, it is not only in the area of photolithographic processing that technology needs to keep innovating. Once a wafer has been created it must be singulated into individual dies, and as dies are becoming smaller and thinner, many products are facing difficulties caused by the singulation or dicing process.

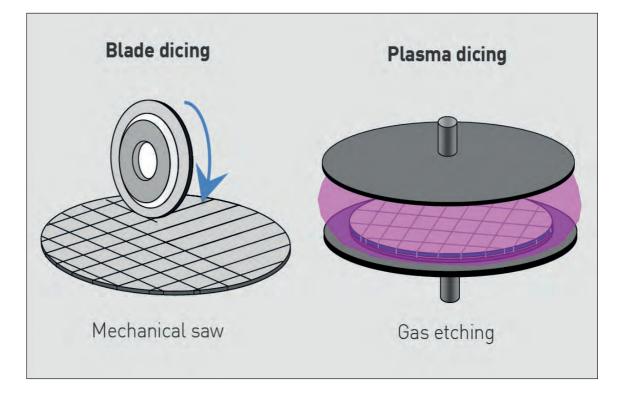

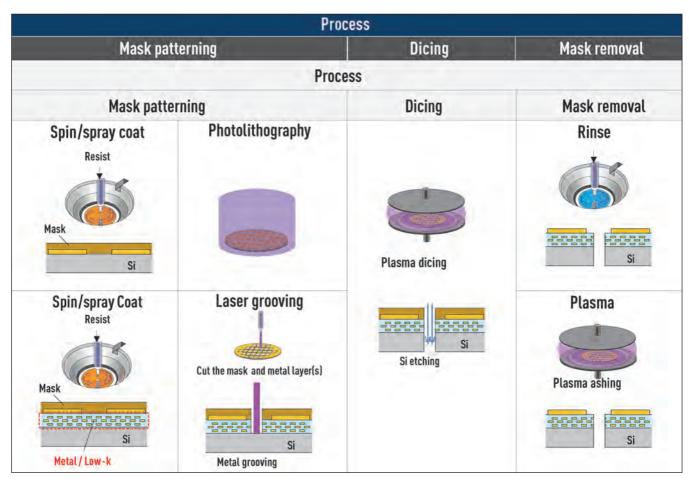

Figure 1: Blade dicing & Plasma dicing processing

### Panasonic Cover Story

Figure 2: Panasonic's chemical etch dicing process

New challenges include: increasing material loss due to the width of the dicing street; mechanical damage such as chipping; and increasing processing time. Now, Panasonic has developed a plasma dicing process that in certain circumstances can replace mechanical dicing, which addresses these issues.

#### Types of dicing process

Traditionally, two dicing technologies have been used: scribing and breaking, and mechanical cutting using a dicing saw ("blade dicing"). Scribing and breaking causes stresses on the wafer and die and results in chipping and yield inefficiencies. Blade dicing also introduces stresses and contaminants which are more problematic as the die size and process geometries shrink. Laser dicing is another method which is faster than using a saw but can also cause cracking and damage to the chip.

Now, a new dicing process has been introduced which uses a plasma chemical etching process, where all the 'cuts' are achieved in a single batch process, with no die stressing, no contamination, and an increase in wafer dicing throughput. Also, more chips can be designed onto the wafer as narrower dicing 'streets' can be used due to mask patterning. In addition, the

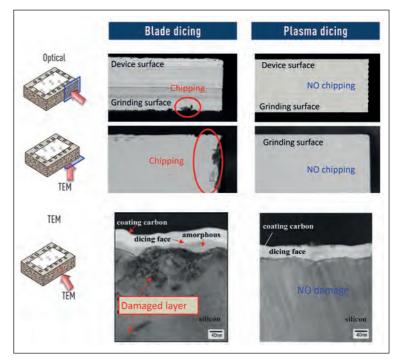

Figure 3: Damage evident on chip samples using blade dicing (left); none present when plasma dicing is used

### Panasonic Cover Story

Figure 4: Strength tests prove the benefits of plasma dicing

mask pattern enables flexibility in the choice of chip sizes, shapes, positioning. The two approaches are shown in Figure 1.

Figure 2 shows Panasonic's plasma dicing process which uses a dicing mask. The plasma process etches the streets by chemical reaction. Plasma dicing uses pulsed or time-multiplexed etching, with the process cycling repeatedly between two phases: a near-isotropic plasma etch where ions attack the wafer in a near-vertical direction; followed by the deposition of a chemically inert passivation layer which protects the entire substrate from further chemical attack.

During etching, the vertically-directed ions attack the passivation layer only at the bottom of the trench (not along the walls), exposing the substrate to the chemical etch. This two-phase process results in sidewalls that increase and decrease with an amplitude of between 100 and 500nm. The cycle time is adjustable: short cycles yield smooth walls; longer cycles yield a higher etch rate.

#### Particle-free and damage-free process

The action of the saw blade during the dicing process causes mechanical damage and affects inner layers of the die. Figure 3 demonstrates damage and chipping at the edge and of the inner layers. By contrast, the micro-photographs show no damage when the individual dies are separated using the plasma dicing process. Also, unlike blade dicing which causes micro particles of the wafer (e.g. silicon) to be freed up, potentially causing devices to fail, by using plasma etching, no contaminating particles are released.

#### Greater chip strength

Chip breakage tests show the typical range of fracture strength for silicon chips to be in the range of 100MPa up to 3000MPa. Dies from several positions on a  $150\mu$ m thick wafer were sampled and a Weibull plot was used to compare the statistical data for chip strengths of lots using blade and plasma dicing preparation methods.

Figure 6: Reduced street widths result in more

| Application Chip size |                                 | Process                      |                           |                           |        |

|-----------------------|---------------------------------|------------------------------|---------------------------|---------------------------|--------|

|                       | Wafer Structure                 | Mask f                       | ormation                  | Dicing                    |        |

|                       | Si<br>Plasma Dicing<br>Si<br>Si | Photolithograp               | bhy<br>Liquid<br>Develop. | Plasma                    |        |

| lmage<br>sensor       |                                 | Mask Patterning Metal/<br>Si | Mask<br>Coating<br>Resist | Laser                     | Plasma |

| Memory<br>/Logic      | Large<br>(3mm~)                 | Plasma Dicing                | Spin or spray<br>coating  | Cut mask &<br>Metal layer | Dicing |

Figure 4 shows that the plasma dicing process results in chips that are about five times stronger than those which underwent blade dicing. With a fracture stress pressure of 600MPa, all samples of chips that had been processed using blade dicing broke due to internal micro- cracks, whereas all of the plasma diced chips shattered at a pressure close to the breakingstrength of silicon. Therefore the plasma dicing process is proven to result in dramatically higher chip strength, especially if thin wafers are being processed.

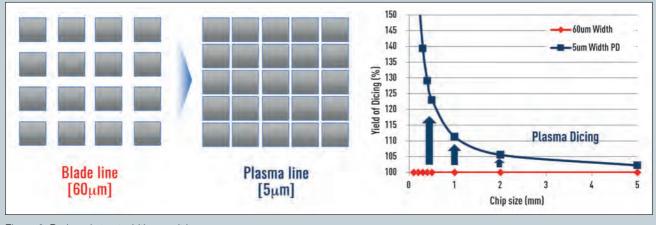

#### Higher throughput and yield

The processing time of blade dicing depends on the number of dicing lines. If the die size is small, longer dicing processing time is required and throughput is reduced. However, with the plasma dicing process, etching is performed across the whole wafer in one pass, so throughput remains constant, no matter how many dicing streets are required (see Figure 5). In addition, the plasma dicing process uses a narrower dicing street design. With blade dicing, there is always a minimum cutting street width, due to the thickness of the blade. A simulation prepared by Panasonic shows that for a 0.5mm<sup>2</sup> chip size, reducing the dicing street width from  $60\mu m$  to  $5\mu m$ , yield will be increased by 23% using the new plasma process (see figure 6). However, the method of avoiding chips contacting other chips when handling a wafer with 5µm dicing street width needs to be considered.

#### Suitability for different wafer processes

The Panasonic plasma dicing process can be applied to wafer dicing with mask patterning either performed

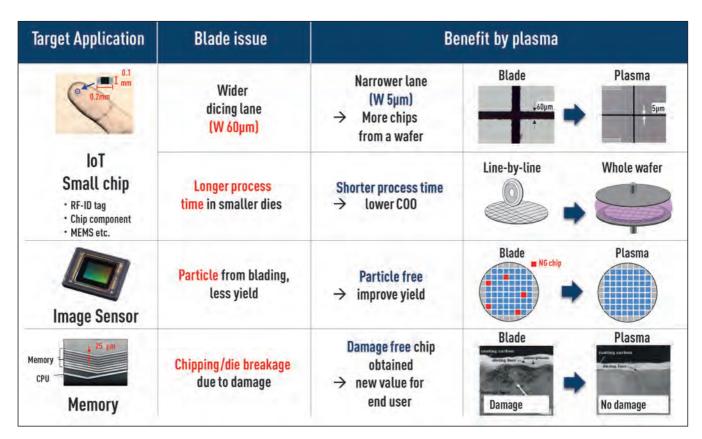

by photolithography or laser patterning methods. The appropriate process flow should be selected to fit the wafer design (Figure 7). Plasma dicing is a high quality innovation which offers different benefits depending on the end application, as shown in Figure 8. In small chips, for example, RFID tags, IoT devices or MEMS sensors, the ability to obtain a higher number of chips per wafer, plus the reduction in process time is paramount. For devices such as image sensors, the elimination of contaminating particles is essential, and the smoother, damage-free sidewalls, with no heat-affected zones or cracking, allows an increase in the active area. For makers of memory ICs, the elimination of damage is most significant.

Panasonic plasma dicing demo center In order to demonstrate the plasma dicing process, Panasonic has built a customer demonstration centre

The processing time of blade dicing depends on the number of dicing lines. If the die size is small, longer dicing processing time is required and throughput is reduced

Figure 7: Panasonic plasma dicing

### Panasonic Cover Story

Figure 8: Benefits of Plasma in Osaka, Japan. This Class 1000 facility is capable of processing 200mm and 300mm diameter wafers with a minimum thickness of  $25\mu$ m. It is fully-equipped including two APX300 plasma dicing machines, laser pattern- ing equipment, polisher / grinder, lithography and measurement equipment, enabling customers to quickly and thoroughly evaluate different products and materials.

#### Total Solutions Approach

In addition to supplying the APX300 Plasma Dicer,

Panasonic is in close contact with vendors globally to assist our customers with the integration and selection of appropriate equipment and material, and implementation of decades of process know-how.

#### Conclusion

Panasonic's plasma dicing process achieves damagefree and particle-free dicing, resulting in inherently stronger chips and increased yield. Throughput is increased and production costs reduced.

|                           | Blade               | Laser               | Plasma         |

|---------------------------|---------------------|---------------------|----------------|

| Dicing method             | Å                   |                     |                |

| Processing time           | X                   | √                   | ✓ Shortest     |

| (8''wafer, t100mm, 🗆 1mm) | (32min / wafer)     | (13min / wafer)     | (7min / wafer) |

| Chip strength             | X                   | √                   | ✓ Highest      |

|                           | (Mechanical damage) | (Mechanical damage) | (Damage free)  |

| Low-k etching             | ×                   | √                   | √              |

|                           | (Wet process)       | (Dry process)       | (Dry process)  |

Figure 9: Summarises the different dicing processes and the advantages of the plasma dicing process

### environments where innovation thrives

edwardsvacuum.com

# Structural defects in

Ultrasound and X-ray work together to image and evaluate harmless anomalies and potential field failures in a TO-220 package.

### BY TOM ADAMS, CONSULTANT, NORDSON SONOSCAN

LAUNCHED by an ultrasonic transducer, a pulse of ultrasound travels through the plastic package of an electronic component at a speed around 3,000 m/s. If it strikes a material interface, there are two possibilities: a) if the interface is be-tween two solids, a portion of the pulse will be reflected back to the transducer and another portion will cross the interface;

or b) if the second material is air, the pulse is almost entirely reflected, and none crosses the interface. The second possibility is useful because most of the internal structural anomalies and future field failures in a component result from cracks, delaminations, voids or other gaps containing air. A few defects that are imaged do not involve air - a tilted die, for example, or a missing solder bump, but both types of interfaces can be located and analyzed by ultrasound.

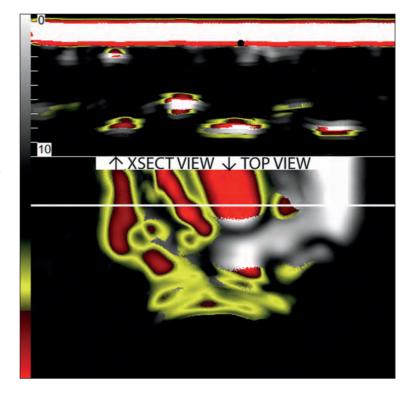

A TO-220 device like the one discussed in this article is designed to be mount-ed by its tab onto a heatsink in order to dissipate large amounts of heat. Internally, wires run from the die, which is mounted on the substrate, upward to the electrical lead posts. The purpose of acoustic micro imaging of this TO-220, carried out by a C-SAM® tool from Nordson SONOSCAN, was to evaluate interfaces for structural defects: the die attach, the bonding of the wires to the die, and the bonding of the wires to the top of the post. A question that could not be resolved by ultrasound was handled by an X-ray tool.

For acoustic imaging, the TO-220 was first flipped over to image the die attach through the metal back side tab, then turned upright to pulse ultrasound through the encapsulate to image first the die face and second, at a higher plane, the top of the post to which the wires were attached.

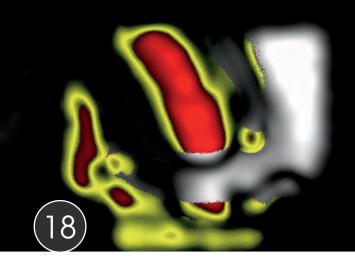

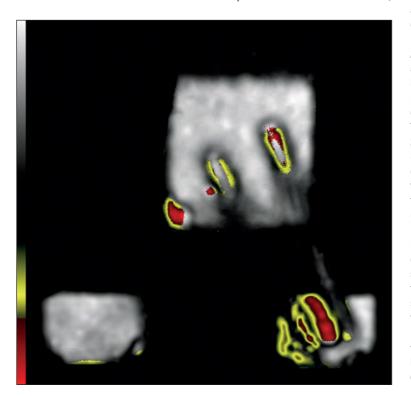

Figure 1: Acoustic image made through the mold compound and showing the die at top and the two posts

At each site, the transducer scanned back and forth a few mm above the area of interest, each second launching thousands of ultrasonic pulses and receiving their return echoes. The echo from each x-y scanned location becomes one pixel in the acoustic image of that area.

From each returning echo the following information is gathered: the echo's acoustic frequency, its amplitude, its polarity, and the depth from which it was reflected. In these images, the colors report amplitude and polarity.

An acoustic image of all three elements in the package is shown in Figure 1. The vertical distance between the die and the posts is too great to be within the same focus. Figure 1 is therefore made from parts of two acoustic images, one focused on each of the two depths within the package.

The right lead attached to the die at top has a very small red area, but the wire bond area is essentially intact. The red area at the lower left corner of the die, however, is a void that could grow with repeated thermal cycles and cause wire bonds to break. Whether this void is enough to cause rejection of the part de-pends on the application. It might be suitable in a commercial application, but perhaps not in a military application.

The two wires visible on the die clearly run to the post at the right. There is no indication in this view of wires running to the left post. In this case the wire has a very fine diameter and is too small to be resolved at the low ultrasonic frequency needed to penetrate the mold compound. There is, however, a faintly brighter area on the left post that somewhat resembles a bonded wire.

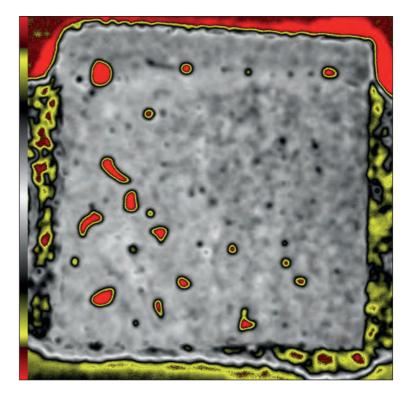

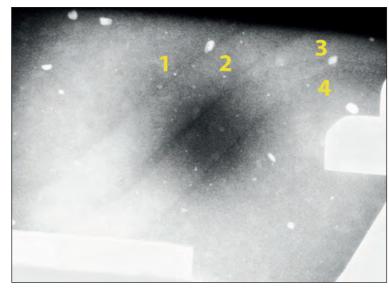

The back side of the die (Figure 2) was imaged through the metal substrate, to which the die is attached. The variously shaped small red features within the area of the die are voids - red here indicates that there is air in the voids. There are no truly dangerous features such as very large delaminations, or voids close to the corners of the die. The voids cover, in total, about four percent of the die area. The TO-220 package is designed to remove large amounts

of heat swiftly, so these relatively small well-spaced voids in the die attach may pose little threat. The problem area in this component, as can be seen in Figure 1, is the right lead post and the wires attached to its top. The red areas are likely voids, but their exact placement and relative danger must be sorted out. To do so, two different imaging modes were used.

The first was a mode that can, during a single scan, image multiple progressively deeper thin slices of the sample being viewed. At each of the thousands or millions of x-y locations in a given image, ultrasound may be reflected from a single interface, or from multiple interfaces at various depths.

To avoid depth confusion, each image is limited to echoes arriving within a specific time that matches a vertical extent within the part. For the right lead post, a total of 6 gates was defined and imaged, each 600 microns in vertical extent. The echoes from each gate became a separate acoustic image. Figure 2: Die attach, as imaged through the bottom of the package

At each site, the transducer scanned back and forth a few mm above the area of interest, each second launching thousands of ultrasonic pulses and receiving their return echoes. The echo from each x-y scanned location becomes one pixel in the acoustic image of that area

Figure 3: The two wires attached to the right post. Red areas are anomalies

Figure 4: Same view, but in a slightly deeper gate

Of the six gates, only gates 3 and 4 revealed details of the two wires and their attachment to the post. In gate 3 (Figure 3). the wire at right is faintly visible. It has no anomalies at this depth except for a small void at its termination. The wire at left has a similar tiny void at its termination, but has a larger void along part of its length.

Gate 4 is seen in Figure 4. The wire at right is very faintly visible. The small void near its tip is visible at this depth. The white area at right is the top of the post to which the two wires are attached. The post extends to the left at least as far as the leftmost void, although it is hidden by overlying features for most of this distance. The large red feature at center is a void, and other voids are scattered about. Red in a delamination or void identifies an area that reflects nearly all of the arriving ultrasound. Red is at the very bottom (=strongest negative echo) in the color map at left. Where the side of a feature becomes steeper and reflects ultrasound less directly in the direction of the transducer, red changes to black. Even steeper sides reflect yellow, the next color on the map.

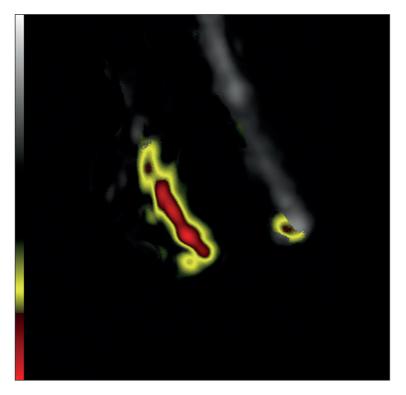

To get an enhanced view of the interior of this device, it was also imaged with the C-SAM's nondestructive cross-sectioning feature called Q-BAM (Quanti-tative B-scan Analysis Mode). A line was described on the acoustic image of the top of the package through which cross-sectioning would cut through the area of the two wires bonded to the lead post. The resulting acoustic cross-sectional image is the dimensionally accurate equivalent of a physical cross sectioning made by cutting down through the package along the same line.

If the sample were physically sawn open along the same line, the same features would be found in the same locations. A light photograph of the sectioned face would look much like the acoustic cross-section. The concept can also be used in a different manner: before physical sectioning, the sample may be imaged acoustically to spot the location through which the physical section will pro-vide the desired information.

The white horizontal line just below the centre of Figure 5 is the line along which the transducer scanned this component in order to produce the acoustic cross-section in the top portion of the Figure. On its first pass along this line, the transducer accepted echoes only from a defined thin depth at the bottom of the package just above the post. The transducer was then raised very slightly and scanned back along the line. By the time it reached the top of the package it had collected the echoes needed to produce the acoustic cross-section seen in the top section of Figure 5.

In the sectional view, the surface of the package is marked by a horizontal red line. In the bottom half, the cross-sections of five features are shown running from left to right. Each feature lies directly above its location

on the thicker white line in the top view below. From left to right, these features are:

- 1. a large air gap on the surface of the post.

- 2. the left wire and the void on top of it.

- 3. the large void to the left of the right wire.

- 4. largely the interface between the mold compound and the post.

- 5. a void at the top of the post itself.

There is a sixth, rather small feature, apparently a void, directly above

6. #1, just below the package surface.

The acoustic images in Figures 1 through 5, however, do not reveal all the wires extending from the die to the posts. The acoustic images revealed two fairly large wires. Smaller diameter wires would be difficult to see because they scatter most ultrasound away from the transducer. In addition, a smaller diam-eter wire might be invisible acoustically at low frequencies. If ultrasound is entirely blocked by an air interface, the wires beneath the air gap will not be imaged.

Subsequently a Dage Quadra 7 X-ray system was used to image the TO-220. An X-ray beam is not stopped or even attenuated by an air gap. Imaging was first attempted through the heat sink, but the thickness of the metal was too great. (Ultrasound would have penetrated the metal but would still have been scattered rather than reflected by the round wires.) to get additional information. The TO-220 was therefore X-rayed from the side, a longer route through the much less attenuating mold compound. The results are seen in Figure 6.

Four wires are visible as vague dark lines marked by numbers in the X-ray image. The image colors have been inverted to make the wires more visible. Their precise orientation cannot be discerned, but it seems likely, taking into consideration the very faint features on the left post in Figure 1, that two wires run from the die to each of the two posts.

Figure 5: Top portion is a non-destructive cross-section through the horizontal white line below the legend

Fig 6: An X-ray beam inserted into the side of the mold compound revealed the four wires

The acoustic images revealed two fairly large wires. Smaller diameter wires would be difficult to see because they scatter most ultrasound away from the transducer

## Ensure wet process cleaning equipment success

Expert consultation can keep semiconductor production on track through installation and beyond.

#### **BY JST**

#### FOR SEMICONDUCTOR MANUFACTURERS,

compound semiconductor manufacturers, raw wafer material suppliers, and R&D labs, utilizing wet process cleaning equipment is critical to producing extremely reliable products, so partnering with a vendor with deep expertise in all aspects of the process – from equipment selection, design specification, testing, and installation/hook up – can be critical to success.

In such fabrication, "cleaning" refers to the etching process used, which precisely removes thin layers of material. In other applications, cleaning can also refer to the use of agents such as solvents, acids or bases to remove unwanted particulates and other contaminates such as photoresist. The cleaning process may involve moving product into extremely hot chemical baths of acids, bases, or flammable solvents, so consulting with an expert can improve safety and ergonomics. It often requires selecting the most appropriate options from a number of technologies. This may involve various chemistries, temperature controls, chemical baths/dips, ergonomic designs, as well as cleaning, filtration, ventilation, safety, and disposal technologies.

It may also involve automating/upgrading the cleaning process for high-volume production. If the process takes place in a cleanroom, then the entire system including motors and robotics must be appropriate for that environment.

Hitting any snag can cause quality or safety issues, delay production, or even cost millions if the equipment must be prematurely replaced to accommodate automation. To avoid these "snags", it can be invaluable to partner with an equipment manufacturer with industry expertise that can help to optimize the entire product life cycle from start to finish.

While all aspects of wet process cleaning are important to consider, failing to plan for even the smallest details of cleaning equipment can lead to challenges like not complying with the local fire or building codes or even being able to get it through doors, hallways or elevators into a clean room.

One area that is often overlooked but can be essential to consider is "facilitization" – meaning the installation, hook up (supplying deionized water, chemistries, drain lines, exhaust system etc.) and safety compliance. Facilitization is a major cost when considering new production equipment and changes in the equipment design to accommodate existing facility constraints can reduce this cost. That is why it is important to work with an equipment supplier that takes the facilitization cost into consideration when quoting a project.

"The facilitization process needs to be thought through because missing important details can cause serious problems that can compromise production and require retrofitting," says Louise Bertagnolli, president of Boise ID-based JST Manufacturing, which designs and manufactures manual and automated cleaning equipment, including proprietary systems with all the features and transfer devices needed for a complete turnkey cleaning process.

As an example, Bertagnolli points to a variety of logistics that must be properly implemented. This can include, for instance, getting the product and chemistries in and out of the tool, and getting the tool into the cleanroom and set up, not to mention meeting safety and exhaust system requirements, etc.

"Because the cleaning equipment can be relatively large, even the size of elevators, doors and hallways

must be checked to ensure it fits," she says. "Failing this, one manufacturer had to have a crane lift the equipment through a 6th story window."

So, to prevent mistakes and ensure that wet process cleaning equipment is designed, installed and "facilitizized" in complete compliance with all safety and performance requirements, it is important for the manufacturer to work with an equipment manufacturer with the expertise to provide one-stop guidance. Getting needed expertise up front ensures that the

wet process cleaning equipment will perform as required, with no unwelcome surprises.

### Planning for success

Specifying for safety and compliance is critical and many aspects need to be sorted through to ensure the tool is designed to be integrated with the semiconductor manufacturing plant.

In terms of complying with fire codes, Bertagnolli says that if the semiconductor manufacturer has its own fire system in a clean room, then the cleaning equipment needs to communicate with it. So, if the tool has an emergency situation

and needs to shut down due to fire, it must notify the house fire alarm system. Fire suppression lines must also be properly sealed and maintain sufficient pressure. Also, to qualify for fire insurance, factory mutual approved materials must be utilized.

When complying with OSHA, she adds that the manufacturer needs to have a three-foot clearance in front of lockout, tag-out areas when powering down for safety. So, this needs to be planned out as well.

According to Bertagnolli, however, there are a number of areas that are prone to mistakes during facilitization if expert guidance is not readily available. In these areas, she suggests that it is particularly important to seek help from an industry expert that can provide one-stop guidance as needed.

For example, to avoid unplanned problems that can delay production and may require expensive retrofits or workarounds, Bertagnolli says that it is necessary to plan for the logistics of the install, down to which elevators, hallways, and doors the wet processing tank/equipment must fit through.

She adds that because many clean rooms have sub floors, it is also necessary to ensure there are structural support/leg levelers on the right floor location. For safety compliance and performance, the manufacturer must also provide sufficient exhaust system air flow velocity, at specific cubic feet per minute rate, designed for the production space.

In addition, facilitization involves correctly hooking up to deionized water, chemistries, and drain lines without any leaks.

"A common error is failing to provide pump pressure to chemistry lines when these need to be brought in from afar," says Bertagnolli. "And per safety codes, dual containment is required on chemical lines."

The chemical line/tank fill systems, in fact, must be configured correctly, or the chemistries will lack sufficient pressure to properly feed the tool or have other issues such as large amounts of entrapped gas. Facility chemical system's with chemical lines that take too many turns, becoming convoluted, can reduce pressure to the point where the tank fails to fill. So, the chemical lines must be configured in a more direct manner that maintains enough pressure to properly supply the tool/fill the tank.

"For facilitization to go off without a hitch, a lot of expertise, planning, and attention to detail has to brought to the project beforehand," says Bertagnolli. According to Bertagnolli, thorough facilitization will even plan for and ease maintenance tasks to avoid unnecessary safety risk or cost.

For example, how a water line runs through the cleanroom should be considered because it can decrease safety and efficiency if it encroaches on the space used to perform maintenance tasks. If planned for, however, the waterline or the cleaning equipment's maintenance space can be located in different, non-conflicting areas.

The bottom line is that for wet process cleaning equipment to be implemented smoothly and correctly, a lot of details need to be expertly determined in order to effectively handle design specification, facilitization and production.

When well-planned with appropriate one-stop guidance, the whole enterprise can get implemented correctly the first time at minimal cost, with production going smoothly far into the future.

Facility chemical system's with chemical lines that take too many turns, becoming convoluted, can reduce pressure to the point where the tank fails to fill. So, the chemical lines must be configured in a more direct manner that maintains enough pressure to properly supply the tool/fill the tank

### Are you onto innovation? We are.

Built upon the rich legacies of Nanometrics and Rudolph Technologies, Onto Innovation stands alone in process control with our unique perspective across the entire semiconductor value chain from bare silicon to leading edge fabs to advanced packaging. We are on a relentless quest to deliver the best comprehensive manufacturing process solutions to the world's most advanced manufacturers through collaboration and innovation.

Onto higher yield Onto higher productivity Onto Innovation

ontoinnovation.com

### Carrier profiling in high vacuum using scanning spreading resistance microscopy and scanning capacitance microscopy

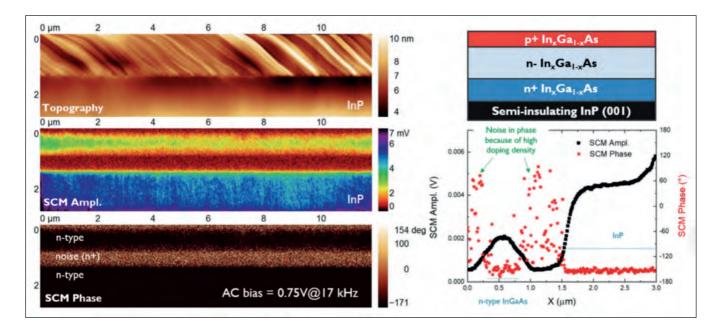

Scanning Spreading Resistance Microscopy (SSRM) and Scanning Capacitance Microscopy (SCM) are both established scanning probe-based methods for two-dimensional carrier profiling. Their initial development was mainly pushed by the microelectronics industry looking for 2D alternatives for their 1D carrier/dopant profiling techniques, such as Capacitance-Voltage (C-V) measurements, Secondary Ion Mass Spectrometry (SIMS), and Scanning Resistance Profiling (SRP).

### BY LENNAERT WOUTERS<sup>1</sup>, ALBERT MINJ<sup>1,2</sup>, UMBERTO CELANO<sup>1</sup>, THOMAS HANTSCHEL<sup>1</sup>, WILFRIED VANDERVORST<sup>1,2</sup>, KRISTOF PAREDIS<sup>1</sup>

IN SSRM, the resistance of the current spreading through the nanoscale tip-sample contact is measured while scanning the probe. The key to its large sensitivity and spatial resolution lies in the presence of a pressure induced metallic pocket below the tip apex resulting in a (nearly) ohmic tip sample contact. As a result, the measured resistance is dominated by the spreading resistance and hence dependent on the local sample resistivity  $\rho$ :

$$R_{spreading} = \rho/4a,$$

Where a represents the contact size. The main advantages of SSRM include a very high spatial resolution ( $\sim 1$  nm) and a large sensitivity and dynamic range ( $10^{14}$ - $10^{20}$  cm<sup>-3</sup>).

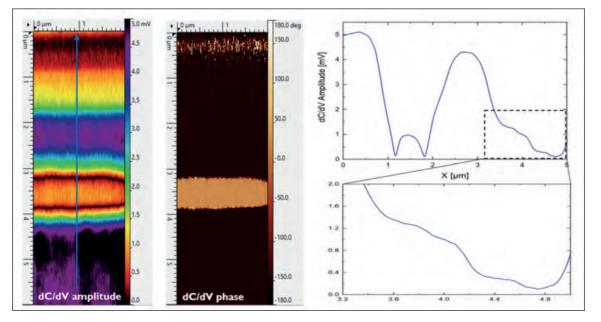

In SCM, small capacitance variations ( $\sim 10^{-21}$  F)

between the tip and the sample are measured using a high frequency capacitance sensor while scanning the probe. Highly doped regions show a low differential capacitance dC/dV, while lowly doped areas exhibit a relatively larger capacitance change. The main advantages are the large dy namic range and the carrier type sensitivity as *n*- and *p*-type show opposite phases in their dC/dV signals.

In both methods, it is not straightforward to convert the measured values directly into quantitative values for carriers because detailed information on the probe and sample surface are missing. Hence, a calibration against a known standard is generally the most straightforward way for converting resistance/differential capacitance to resistivity/carrier concentrations.

In fact, both techniques exhibit pros and cons, but are quite complementary; SSRM provides the highest spatial resolution while SCM provides carrier type sensitivity.

<sup>1.</sup> IMEC, Leuven, Belgium,

<sup>2.</sup> Department of Physics and Astronomy, University of Leuven, Leuven, Belgium)

### IMEC / Park Systems

As current state-of-the-art devices are entering the sub 10 nm nodes, the requirements for materials and device characterization are being pushed to their limits, requiring every aspect of the measurement to be optimized for successful measurements, for instance the probe, the sample preparation, and the measurement environment.

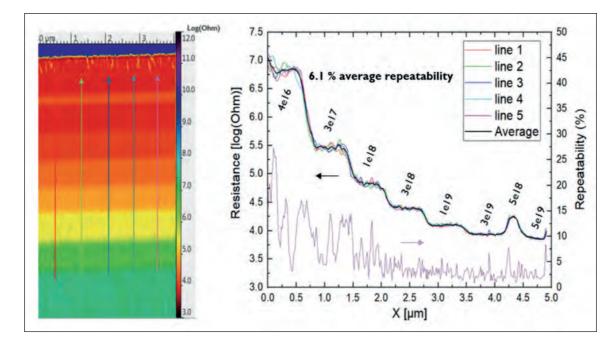

In this application note, we review the performance of the Park NX-Hivac atomic force microscope (AFM) from Park Systems [1] for SSRM and SCM applications, based on the following three samples:

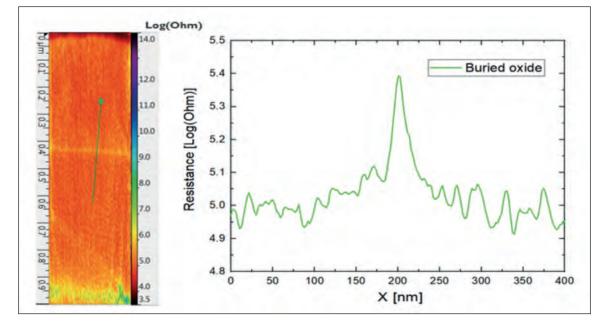

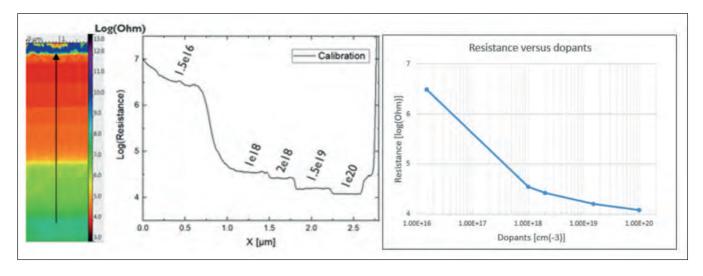

A p-type doped silicon calibration sample (imec CS08-SiB): a sample consisting of various Boron doped epitaxial silicon layers (~600 nm) with known doping concentration (Figure 1).  An n-type doped silicon calibration sample (imec CS01-SiAs): a sample consisting of various arsenic doped epitaxial silicon layers with known doping concentration (Figure 5). This sample additionally has a *p*-type doped layer embedded in the stack.

3. Buried oxide sample: a 0.5 nm oxide layer sandwiched in between a highly doped Si and a poly Si layer (Figure 2).

These samples are measured on the Park NX-Hivac AFM system, operating in vacuum conditions (~5e<sup>-5</sup> mbar) using imec Full Diamond probes [2].

#### SSRM - Basic performance

Firstly, the p-type calibration sample is measured to investigate the repeatability of SSRM measurements.

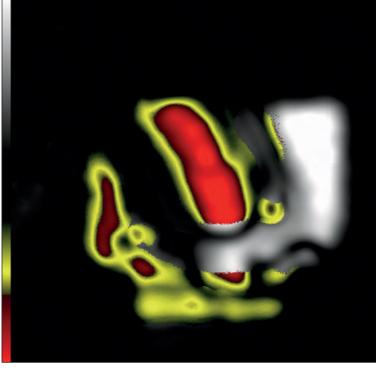

Figure 1: SSRM measurement on a *p*-type doped silicon calibration sample performed in vacuum. The coloured resistance cross-sections are taken from single line scans and the black line is the average over those 5 scan lines. The repeatability is plotted in purple (right Y-axis).

Figure 2: High resolution SSRM measurement on a 0.5 nm oxide layer sandwiched in between highly doped Si and poly Si layers. The resistance cross-section is taken from a single scan line.

### IMEC / Park Systems

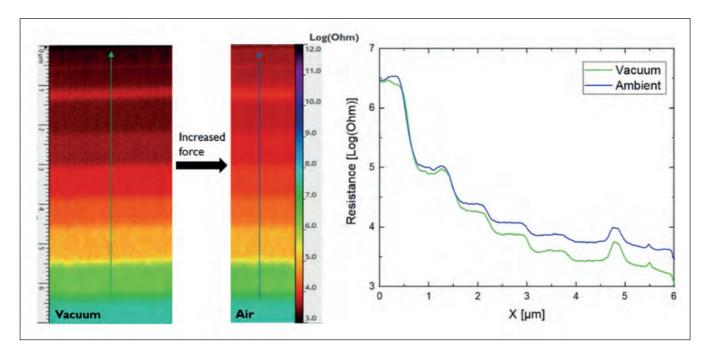

Figure 3: SSRM measurements on a *p*-type doped silicon calibration sample performed in vacuum and in air with the same probe. The resistance cross-sections are the average over 50 scan lines.

Figure 1 shows that excellent repeatability is achieved in SSRM measurements on silicon. Note that the repeatability is better in the highly doped layers. As a reference, for identical scanning parameters, typically a repeatability of 15-20 % is achieved in air highlighting the added value of high vacuum [3].

Secondly, to assess the resolution of SSRM the buried oxide sample is measured. Figure 2 demonstrates that the 0.5 nm oxide layer embedded in silicon can easily be observed in SSRM measurements as an increase in the resistance. The doubling of the resistance on the thin oxide indicates that the electrical contact radius is similar as the oxide thickness, highlighting a sub-nm resolution [2].

Finally, the p-type calibration sample is measured in air and in vacuum with the same probe to verify the advantages of performing SSRM measurements in a vacuum environment. The results are summarized in Figure3. As expected, in order to obtain an image of similar quality, the applied force to the tip required for a good electrical tip-sample contact had to be increased by almost 50 % when moving from vacuum to ambient environment. This observation suggests that the metallic pocket below the tip apex is induced

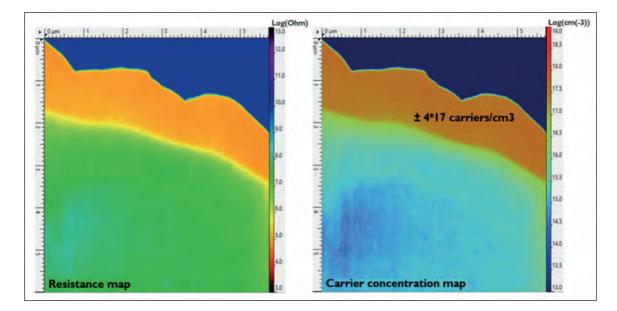

Figure 4: SSRM resistance and carrier concentration maps of an *n*-type doped silicon layer in a solar cell sample.

Figure 5: SSRM measurement on an *n*-type doped silicon calibration sample. The resistance cross-section is taken from the average of 50 scan lines. The resistance versus dopants data points are taken from the average resistance values measured over the 5 layers with known doping levels in the calibration sample.

at a lower pressure in vacuum as compared to in air. Therefore, measurements in vacuum environment can be performed with a lower force applied to the tip which will result in less tip wear and thus higher resolution [2].

From the results shown above it can be concluded that the repeatability and resolution of SSRM measurements performed on the Park NX-Hivac AFM are state of the art, and that the vacuum conditions in the chamber are beneficial for conducting repeatable SSRM experiments.

### SSRM - Device measurements & calibration

In general, the calibration samples allow to convert the resistance map of an unknown sample to a carrier concentration map. To do so, the calibration sample is measured with the same probe and scan parameters as the measurement on the sample of interest. As an example, in Figure 4, the resistance and carrier concentration maps of an n-type doped silicon layer in a solar cell are shown.

The carrier concentration map is calculated from the resistance map by using the calibration curve that is shown in Figure 5. The resistance data points are taken from the average resistance values measured over the 5 layers with known doping levels. The calibration curve is obtained by interpolation of these data points.

It can be concluded that the good measurement repeatability on both the sample and the standard

Figure 6: SCM dC/ dV amplitude and phase measurements on an *n*-type doped silicon calibration sample.

### IMEC / Park Systems

Figure 7: SCM measurement on a doped InGaAs stack. The dC/dV amplitude and phase cross-sections are taken from the average of 100 scan lines.

allows for an accurate determination of the active carrier concentration in a sample with unknown carrier levels.

#### **SCM**

The n-type doped silicon calibration sample is used to evaluate the performance of SCM on the Park NX-Hivac AFM. This sample has, next to the *n*-type epitaxial layers, also a *p*-type doped layer in between the substrate and the *n*-layers.

Figure 6 shows respectively the dC/dV amplitude and the dC/dV phase map obtained from an SCM measurement on the n-type calibration sample. From the phase map, one can clearly distinguish the n and p-layers.

The various *n*-type layers with different doping concentrations show also a clear contrast in the dC/dV amplitude map. These results demonstrate the carrier concentration sensitivity and the carrier type sensing capability of SCM, even though the spatial resolution is not as good as in SSRM.

The dC/dVamplitude cross-sectionis taken from the average of 50 scan lines. Besides Si, another interesting application of SCM is on III-V material stacks. In Figure 7 the results of an SCM measurement on a doped InGaAs stack are shown and they allow to extract information about the carrier concentration and the carrier type.

#### Conclusions

This study shows that scanning spreading resistance microscopy (SSRM) and the scanning capacitance microscopy (SCM) can meet the challenges of carrier profiling the state-of-the-art devices entering the sub 10 nm nodes given the right microscopy tool. This investigation found that Park NX-Hivac is the powerful tool that meets the challenges of ever shrinking devices with its implementation of electrical SPM modes, including SSRM and SCM, in a high vacuum environment. Furthermore, we conclude that the use of Park NX-Hivac vacuum aids significantly to reduce the noise, resulting in an average repeatability of 6.1 % for SSRM measurements.

#### References

- [1] Park NX-Hivac, Retrieved from https://parksystems.com/products/small-sample-afm/park-nx-hivac?highli ght=WyJueC1oaXZhYyIsIm54LWhpdmFjJ3MiXQ==

- [2] Hantschel, T., et al. Diamond scanning probes with sub-nanometer resolution for advanced nanoelectronics device characterization, Microelectronic Engineering 159, 46-50 (2016).

- [3] Eyben, P. et al. Fundamentals of Picoscience, Subnanometer Characterization of Nanoelectronic devices. Edited by Sattler, K.D., CRC Press (2014)

### Siconnex BATCHSPRAY<sup>®</sup> Technology.

(0 \_ (\*

Our innovative BATCHSPRAY® technology is based on a closed system, in which wet chemical cleaning and etching processes are performed highly efficiently. Various chemical processes, including rinsing and drying, are performed fully automatically in a process chamber.

UK

#### **ADVANTAGES**

Automated dry-in, dry-out process

- High throughput, due to 25 or 50 wafer chamberSmall footprint (~ 25 sqft)

- For 2" to 12" substrates

- Manual or automated robot loading with the patented Retainer Comb Handling (RCH) System (FOUP, SMIF, etc. compatible)

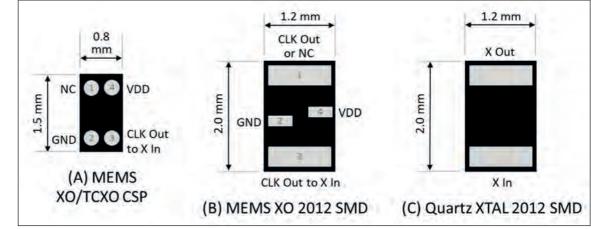

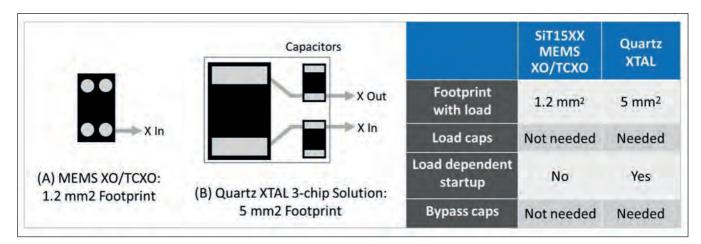

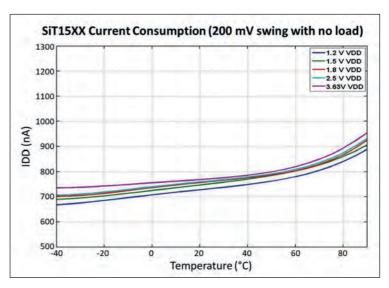

### **MEMS oscillators:** enabling smaller, lower-power IoT & wearables

SiTimes makes a case for MEMS oscillators versus quartz-crystal-based clocking sources.

### BY JEHANGIR PARVERESHI, SR. MANAGER, CUSTOMER ENGINEERING AND HARPREET CHOHAN, DIRECTOR, MARKETING

THE EXPLOSIVE GROWTH in internet-connected devices, or the internet of things (IoT), is driven by the convergence of people, devices and data across the web. Future growth will be strongly influenced by wearable technology as products transition from the laptop to the pocket to the body. Activity trackers are leading this segment in the number of units shipped per year, followed by smart watches and medical monitors/devices, as well as wearable cameras and smart glasses. These devices are enabled by advancements in MEMS and sensor technology, wireless connectivity and new power savings capability.

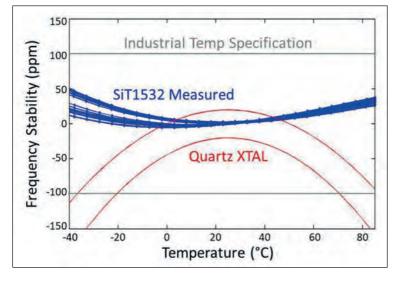

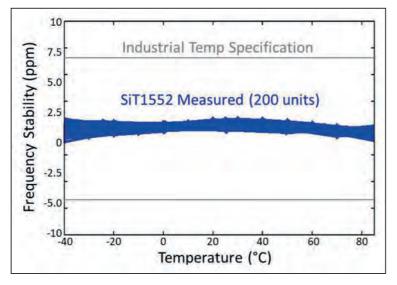

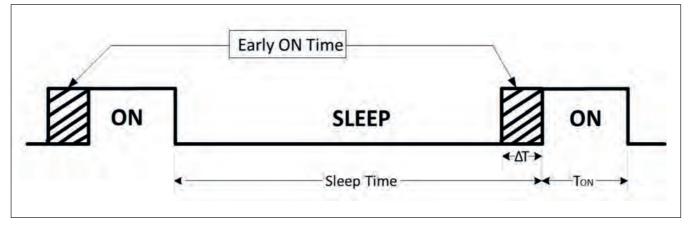

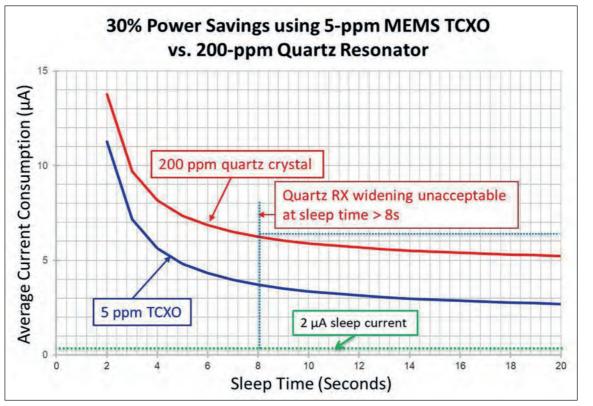

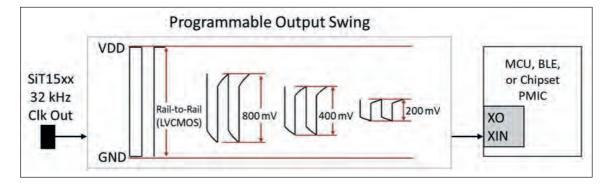

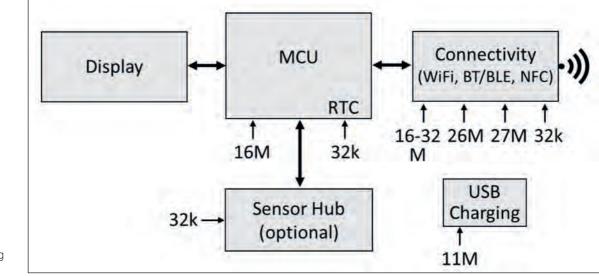

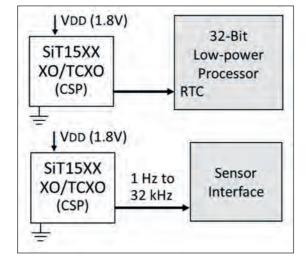

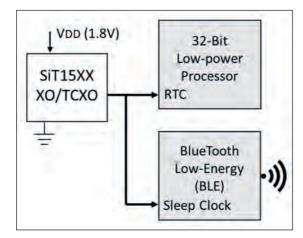

### Wearable devices leverage new timing technology